SOFTWARE FOR A REAL-TIME DIGITAL SIGNAL PROCESSOR

Lawrence M.L.Casserley

Royal College of Music, London

### INTRODUCTION

A low-cost programmable digital signal processor has been developed, which enables real-time audio transformations to be effected. The board can be interfaced to a PCM recorder and a microcomputer to provide an economical signal processing package with applications in sound recording, electro-acoustic music, acoustic research, etc. A brief description of the system is given, followed by a discussion of some practical software for the processor. The paper also illustrates how these program modules may be combined to form practical devices.

### PHI HARDWARE OVERVIEW

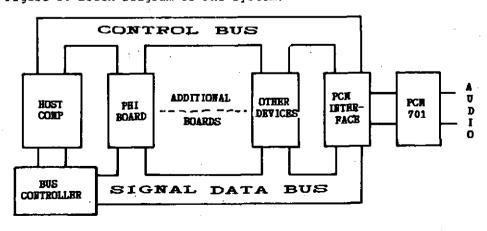

A block diagram of the system, known as SERIES PHI, is given in Figure 1. One or more PHI processor boards are connected to two independent busses. The first, the Control Bus, is used to download programs and control data from the host computer. The second, the Signal Data Bus carries audio samples between PHI processors, AtoD and DtoA converters and other devices, eg long delay memory. At present an interface card to a Sony PCM-701 Digital Audio Processor provides two channels of 16 bit AtoD and DtoA conversion as well as direct access to and from digital tape. Other types of conversion could, however, be used. With this interface the system is locked to the 44.1KHz sampling rate of the PCM.

Figure 1. Block Diagram of PHI system.

### SOFTWARE FOR A REAL-TIME DIGITAL SIGNAL PROCESSOR

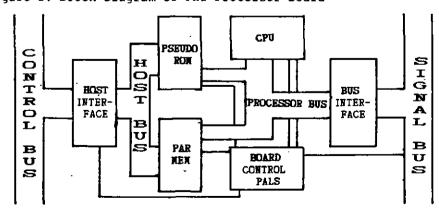

A block diagram of the PHI processor board is shown in figure 2. The CPU is a Texas TMS32010 16/32 bit Signal Processor chip. Two separate memories are used. The first appears as ROM to the 32010, but can be written into by the host computer. This is used for storing programs and wave tables and occupies the normal address space of the 32010. The second memory is accessed via two of the 32010's I/O ports and is used for passing dynamic parameters and for storing delayed samples beyond what can be stored in the 32010's internal memory. On the prototype approximately 100ms of delay is available. Longer delays will be handled off board by a separate delay memory system being developed. The use of both these memories and a number of other features of the PHI Processor Board will be demonstrated in the following discussion.

#### PHI SOFTWARE EXAMPLE

Figure 3 gives the assembler listing for an example program, MODUL1. This illustrates a typical electro-acoustic music application. The signal from an AtoD converter is low-pass filtered and ring-modulated with a sine wave, then reverberation is added before sending the result to a DtoA converter.

The first two lines of the listing define the function as a series of linked macros, which are expanded below. The figures in the left-hand column are instruction cycles. The 5 MHz instruction rate of the 32010 allows 112 instruction cycles per sample, and the assembler automatically keeps a running count of instruction cycles used.

Instruction 003 loads the input from Port 0; the assembler will generate a link map for the Signal Data Bus which will route ADCO to Port 0. The symbols 'OP' and 'IP' are reserved in the PHI assembler to indicate the outputs and inputs of macro 'devices' which are linked according to the function definition at the beginning of the code.

Figure 2. Block Diagram of PHI Processor Board

### SOFTWARE FOR A REAL-TIME DIGITAL SIGNAL PROCESSOR

### Low Pass Filter

Instruction 005 begins the code for a third order Chebyshev low pass filter[1]. First, a block of data is defined to hold the delayed samples. This ensures that they are in the correct order for most efficient implementation by the 32010. Next the coefficients are defined as parameters. The code illustrates use of the 32010's pipelining facilities. The instruction 'LTD' loads a new data word into the multiplier, accumulates the previous result and shifts the data to the next address in memory (hence the necessity to specify a precise data structure). Thus a filter of this kind can be implemented in two instruction periods per term plus three (zero accumulator to start, accumulate and store the final result to finish), a total of 17 in this case. Six such filter segments could be implemented on one PHI board.

### Sine Wave Generator

The next segment of code beginning with the label SGEN implements a basic generator. The version shown assumes a half cycle sine (or other) table is stored in main memory. This is adressed by the lower twelve bits of the the accumulator during the 'TBLR' (table read) instruction. The current phase angle and phase increment are stored as double word variables allowing 28 bit resolution in the phase calculations. The code at 035 determines which half of the cycle is current and the final four instructions allow amplitude control. This generator is somewhat more demanding of processor time, requiring 24 instruction periods, but could be simplified for less demanding applications by using only 16 bit precision and a whole cycle wave table.

### Ring Modulator

By contrast this is extremely simple, in fact identical with the level controller at the end of the generator segment. In the former case it acts as an amplitude modulator as long as the 'LEVEL' parameter is constrained to be a positive number. It also depends on the assumption that both inputs have no offset component.

#### Reverberation

The reverberation algorithm utilises a tapped delay line in the upper part of parameter memory. The number of taps is selected to fill the remaining processor time, in this case three are possible. The quality of reverberation is therefore somewhat dependent on what else is being done, but, in a programmable system, these options, like the choice of generator complexity, are made available to the user.

The function is implemented in four sections. First the new table addresses are calculated. Note that program iterations are used in preference to a subroutine which only wastes time in this context. Next the data transfers occur. Note that the board architecture uses two I/O ports named PARCAPT and PARREL writing to PARCAPT loads a new address and "captures" the memory, preventing a host write from interfering with the transfer. Reading from or writing to PARREL transfers data and "releases" the memory into control of

#### SOFTWARE FOR A REAL-TIME DIGITAL SIGNAL PROCESSOR

the host once again. Reading from PARCAPT, however, also transfers data but keeps the memory "captured" so that a write to the same address can follow immediately. In this way the new sample is written in the same position as the final tap. Next the delayed samples are weighted and accumulated in the same manner as in the low pass filter. Finally the reverberation product and the direct signal are mixed and sent to the DAC.

The last part of the code implements a counter in one of the 32010's Auxiliary registers, which is used to control the transfer of parameters at a rate of one per sample. This code is included in all programs automatically by the PHI assembler.

### HOST SOFTWARE

PHIASM is an interactive editor/assembler which is designed to make the development of programs for the PHI Processor relatively straightforward. Since the code is necessarily short, it keeps both source and object files in memory and flags potential errors as they are entered. It deals with all memory allocations and automatically generates link maps for the Signal Data Bus and Parameter Memory for use by the run-time controller. It also keeps track of the number of instruction periods in use and pads unused time with NOPs.

PHIPER is a run-time system which sets up the performance environment, downloads programs and parameter data and sets up the Signal Data Bus link map. It is designed to allow the interfacing of a variety of control devices suitable to different applications. Other program generation and run-time control software is planned.

### CONCLUSION

The PHI system has been developed over a number of years for the author's own use as a performing musician. While the 112 instructions/sample rate of the PHI system presents some restrictions, it can be seen from the above discussion that such a device can implement viable and useful functions. The use of more than one board in a system quickly increases the sophistication of the possible sound transformations. Above all, its programmability makes the system capable of implementing many different functions, so that one unit can be equivalent to many individual devices.

[1]. I am indebted to Per Hartmann for assistance with the mathematics of the Chebyshev filter.

## SOFTWARE FOR A REAL-TIME DIGITAL SIGNAL PROCESSOR

| Figure 3. Example Program Listing - MODUL1                                                                   |             |                                                                      |                                                                          |                    |  |  |

|--------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|--|--|

| 000                                                                                                          | &FMODUL1    | ADC0>CHLPF>RMOD(1)>REV4>DAC0<br>SGEN>RMOD(2),                        |                                                                          |                    |  |  |

|                                                                                                              | &X          |                                                                      |                                                                          |                    |  |  |

| 000<br>002                                                                                                   | PARLOAD:    | IN<br>EINT                                                           | *,PREL                                                                   | ;input parameter   |  |  |

| 003                                                                                                          | ADC0:       | IN                                                                   | OP, PORTO                                                                | get sample;        |  |  |

| 005                                                                                                          | CHLPF:      | IPM3<br>IPM2<br>IPM1<br>IP<br>OPM2<br>OPM1<br>OP                     |                                                                          | ;define data block |  |  |

|                                                                                                              | &P          | COEF1<br>COEF2<br>COEF3<br>COEF4<br>COEF5<br>COEF6<br>COEF7          |                                                                          | ;define parameters |  |  |

| 005<br>006<br>007<br>008<br>009<br>010<br>011<br>012<br>013<br>014<br>015<br>016<br>017<br>018<br>019<br>020 |             | ZAC LT MPY LTD MPY LTD MPY LTA MPY LTA MPY LTA MPY LTD MPY APAC SACH | IPM3 COEF4 IPM2 COEF3 IPM1 COEF2 IP COEF1 OPM2 COEF7 OPM1 COEF6 OP COEF5 | ;filter algorithm  |  |  |

| 022                                                                                                          | SGEN:<br>&P | &DPHINC<br>LIMIT<br>BASE<br>LEVEL                                    |                                                                          | ;define parameters |  |  |

### SOFTWARE FOR A REAL-TIME DIGITAL SIGNAL PROCESSOR

| 022<br>023<br>024<br>025<br>026<br>027<br>028<br>029<br>030<br>031<br>035<br>036<br>037<br>040<br>041<br>042<br>043<br>044<br>045 | SCALE: RMOD: | ZALH ADDS ADDH ADDS SACH SACL LAC AND SACL OR TBLR LAC SUB BLZ ZAC SUB SACL LT MPY PAC SACH LT MPY PAC SACH | PHANG PHANG + 1 PHINC PHINC + 1 PHANG, 0 PHANG + 1 PHANG LIMIT PHANG BASE SAMPLE PHANG BASE SCALE SAMPLE | ;update phase angle ;prevent overflow ;must be pwr of 2 ;which half cycle? ;negate sample ;level control ;must be positive ;4 quadrant mult |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 049                                                                                                                               | REV4:<br>&P  | DEL1 DEL2 DELEND TABLENI OFFSET TESTER DIRLEVE COEF1 COEF2 COEF3 COEF4                                      | EL .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ;define parameters ;end of storage ;start of storage ;equals offset + 1                                                                     |

| 050<br>051<br>052<br>054<br>055<br>056<br>057<br>058<br>059<br>061<br>062                                                         | RESULT1:     | LAC<br>SUB<br>BGEZ<br>ADD<br>ADD<br>SACL<br>LAC<br>SUB<br>BGEZ<br>ADD<br>ADD<br>SACL                        | DEL1,0 TESTER,0 RESULT1 TABLEND,0 OFFSET,0 DEL1 DEL2,0 TESTER,0 RESULT2 TABLEND,0 OFFSET,0 DEL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ;advance pointer;<br>rpt for each tap                                                                                                       |

### SOFTWARE FOR A REAL-TIME DIGITAL SIGNAL PROCESSOR

| 064<br>065<br>064<br>066<br>067<br>068<br>069<br>071<br>073<br>075<br>077 | RESULT3: | LAC SUB BGEZ ADD ADD SACL OUT IN OUT IN OUT IN | DELEND, 0 TESTER, 0 RESULT3 TABLEND, 0 OFFSET, 0 DELEND DEL1, PARCAPT DDAT1, PARCAPT DDAT2, PARCAPT DDAT2, PARCAPT DELEND, PARCAPT DDAT3, PARCAPT | get data;                       |

|---------------------------------------------------------------------------|----------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 081<br>083<br>084<br>085                                                  |          | OUT<br>ZAC<br>LT<br>MPY                        | IP, PARREL  DDAT1 COEF1                                                                                                                           | ;accumulate delays              |

| 086<br>087<br>088                                                         |          | LTA<br>MPY<br>LTA                              | DDAT2<br>COEF2<br>DDAT3                                                                                                                           |                                 |

| 089<br>090<br>091                                                         | •        | MPY<br>LTA<br>MPY                              | COEF3<br>DDAT4<br>COEF4                                                                                                                           |                                 |

| 092<br>093<br>094                                                         |          | LTA<br>MPY<br>APAC                             | IP<br>DIRLEVEL                                                                                                                                    | ;mix input                      |

| 095                                                                       |          | SACH                                           | OP,1                                                                                                                                              | . 1                             |

| 096                                                                       | DAC0:    | OUT                                            | IP,PORTO                                                                                                                                          | ;result to DAC                  |

| 097                                                                       | PADNOP:  |                                                | _1                                                                                                                                                | ;pad with NOPs                  |

| 109<br>110<br>111<br>112<br>113                                           | PARADDR: | OUT<br>BANZ<br>LAR<br>NOP                      | SAR ARO, PA<br>PARCAPT, PAD<br>END<br>ARO, NOPARS                                                                                                 | D;ARO points to ;next parameter |

| 113                                                                       | LIID.    |                                                |                                                                                                                                                   |                                 |